# Static Synchronous Series Compensator for Improved Voltage stability and Dampen Power Oscillations in Transmission Line

S. Chandra Sekhar1

G. VenkataSubba Reddy2

(M. Tech) Student

Asst. Professor (M.Tech)

G. Pulla Reddy Engineering College

Kurnool, Andhra Pradesh, India

Abstract— This paper investigates the problem of controlling and modulating power flow in a transmission line using a Synchronous Static Series Compensator (SSSC). The studies, which include detailed techniques of twelve pulse and PWM controlled SSSC, are conducted and the control circuits are presented. The developed control strategies for both twelve-pulse and PWM-controlled SSSC use direct manipulations of control variables instead of typical d-q transformations. The complete digital simulation of the SSSC within the power system is performed in the MATLAB/Simulink. Simulation results validate that Voltage and Power Oscillation can be damped properly using of Synchronous Static Series Compensator (SSSC).

Index Terms— SSSC, Reactive compensation, Control strategy, FACTS, PWM control and voltage stabilization.

#### I. INTRODUCTION

In the last decade, commercial availability of Gate Turn-Off (GTO) thyristor switching devices with high power handling capability and the advancement of the other types of power-semiconductor devices such as IGBTs have led to the development of fast controllable reactive power sources utilizing new electronic switching and converter technology. These switching technologies additionally offer considerable advantages over existing methods in terms of space reductions and fast effective damping [1]. The advent of FACTS systems is giving rise to a new family of power electronic equipment for controlling and optimizing the dynamic performance of power system, e.g., STATCOM, SSSC, and UPFC. The use of voltage-source inverter (VSI) has been widely accepted as the next generation of flexible reactive power compensation to replace other conventional VAR compensation, such as the thyristor-switched capacitor (TSC) and thyristor controlled reactor (TCR) [2,3]. The SSSC controller consists of a solid-state VSC with several GTO thyristor switches, or any other semiconductor switches with intrinsic turn-off capability valves, a dc capacitor, a transformer, and a controller. It is important to note that several of the VSCs can be connected together through a transformer of sometimes a complex and custom made design configuration. The number of valves and the various configurations of the transformer depend on the desired quality of ac waveforms generated by the SSSC [4,5]. The line side transformer winding is connected in series, placing the VSC also effectively in series with a transmission

line, and thus allowing series compensation of the line. The SSSC is used to generate or absorb reactive power from the line, and hence can be utilized as a transmission line power flow controller. Basically, it generates on its output terminals a quasi-sinusoidal voltage of variable magnitude in quadrature with the transmission line current, if the SSSC losses are neglected. Thus, the line injected voltage emulates a capacitive or an inductive reactance in series with a transmission line, which increases or decreases the

total transmission line reactance, resulting in a decrease or increase of the power flow in the transmission line [6]. In general, the SSSC can be viewed as analogous to an ideal synchronous voltage Source as it can produce a set of three-phase ac voltages at the desired fundamental frequency of variable and controllable amplitude and phase angle. It also resembles a synchronous compensator, as it can generate or absorb reactive power from a power system and can, independently from the reactive power, generate or absorb real power if an energy storage device instead of the dc capacitor is used in the SSSC. The SSSC is typically restricted to only reactive power exchange with the nearby ac system, neglecting the small amount of real power used to cover the circuit and switching losses, because of the relatively small SSSC capacitor. If the dc capacitor were replaced with an energy storage system, the controller would be able to exchange real power with the ac system and compensate for the transmission line resistance [7, 8].

#### II. BASIC OPERATING PRINCIPLES OF THE SSSC

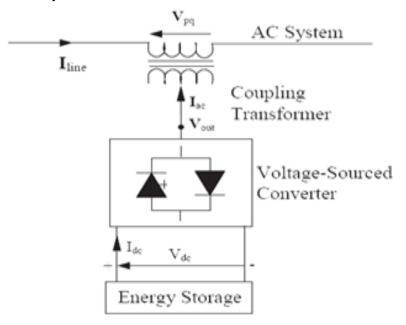

Fig.1 shows a functional model of the SSSC where the dc capacitor has been replaced by an energy storage device such as a high energy battery installation to allow active as well as reactive power exchanges with the ac system. The SSSC's output voltage magnitude and phase angle can be varied in a controlled manner to influence power flows in a transmission line. The phase displacement of the inserted voltage  $V_{pq}$ , with respect to the transmission line current *Iline*, determines the exchange of real and reactive power with the ac system.

FIG 1. FUNCTIONAL MODEL OF SSSC

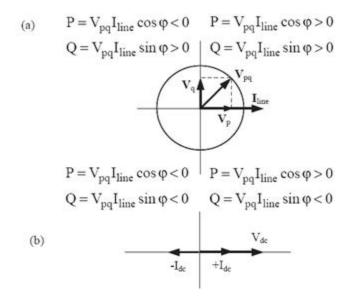

Fig. 2 shows the SSSC operation in four quadrants, again assuming an energy storage device connected at the SSSC's input terminals. The line current phasor Iline is used as a reference phasor while the injected SSSC voltage phasor is allowed to rotate around the center of the circle defined by the maximum inserted voltage  $V_{pq}^{max}$ .

FIG 2. SSSC PHASOR DIAGRAM

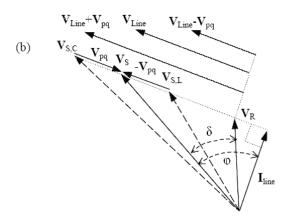

Theoretically, SSSC operation in each of the four quadrants is possible, Theoretically, SSSC operation in each of the four quadrants is possible, but there are some limitations to the injected SSSC voltage due to operating constraints of practical power system. In capacitive mode, the injected SSSC voltage is made to lag the transmission line current by90°; in this case, the SSSC operation is similar to the operation of a series capacitor with variable capacitance kXc, i.e.  $V_{pq} = -jKX_c I_{line}$ , where k is a variable. By this action, the total transmission line reactance is reduced while the voltage across the impedance is increased, leading to increase in the line currents and transmitted power. This action is illustrated in Fig. 3.It is also possible to reverse the injected SSSC voltage by  $180^{\circ}$ ,  $-V_{pq} = jKX_c I_{line}$  causing an increase in the transmission line reactance, which results in a decrease of the line current and transmitted power. While this equation for pq V shows changes in the phasor magnitude and phase angle, it can be somewhat misleading, since it shows that the series injected voltage magnitude is directly proportional to the line current magnitude. In reality, this is not true; the inserted voltage magnitude is set by the SSSC control and is independent of the network impedance and, consequently, line current changes. In Fig. 3, it is assumed that the SSSC losses are zero and, therefore, the series injected voltage is in perfect quadrature with the line current, leading or lagging.

The operating conditions that limit the SSSC operation from the power system point of view are also depicted in Fig. 3 The SSSC can increase as well as decrease the power flow in the transmission line by simply reversing the operation from capacitive to inductive mode. In the inductive mode, the series injected voltage is in phase with the voltage drop developed across the line reactance; thus, the series compensation has the same effect as increasing the line reactance. If the series inserted voltage magnitude is larger than voltage drop across the uncompensated line, i.e.,  $V_{pq} \ge V_{line}$ , the power flow will reverse. This fact can limit the SSSC operation to values of  $V_{pq} \le V_{line}$ , as in practice, it would be unlikely to use the SSSC for power reversal. Also, if the rating of the SSSC controller is high, it is possible to increase or decrease the receiving end voltage above or below the typical operating voltage range of 0.95p.u. – 1.05 p.u, but with possible negative consequences for other system devices.

The SSSC output current corresponds to the transmission line current, which is affected by power system impedance, loading and voltage profile, as well as by the actions of the SSSC. Thus, the relationship between the SSSC and the line current is complex. The fundamental component of the SSSC output voltage magnitude is, on the other hand, directly related to the dc voltage that is either constant or kept within certain limits, depending on the chosen design and control of the SSSC. The SSSC output

voltage phase angle is correlated to the line current phase angle by plus or minus few degrees for example, to account for changes in the dc voltage. It has to be noted that the injected SSSC voltage Vpq is different from the SSSC output voltage Vsssc, due to the voltage drop or rise across the series transformer reactance, i.e.,

$$V_{pq} = V_{sssc} \pm X_{tr} I_{line}$$

.

where the minus sign corresponds to capacitive operation, while the positive sign corresponds to inductive operation of the SSSC and Xtr stands for the series transformer reactance. This voltage difference between the injected and output SSSC voltage can be small in the case of small transmission line currents, but it can be significant in high loading conditions.

The active and reactive power exchanged between the SSSC and the transmission line can be calculated as follows:

$$P_{pq} = V_{pq}. I_{line} Cos \psi$$

(2)

$$P_{pq} = V_{pq}. I_{line} Sin \psi$$

(3)

where  $\psi$  represents the angle between the injected SSSC voltage and transmission line current.

Fig 3. Series compensation by a SSSC

Inspection of the equations (2) and (3), considering that the angle between the SSSC output voltage and line current is approximately 90  $^{\circ}$ , shows that the SSSC real power should be small compared to the reactive power. This is expected, since the real power going into the SSSC is used only to cover for the losses and charging of the dc capacitor, i.e.,

$$P_{pq} = P_{dc} + P_{losses} \tag{4}$$

The losses in the SSSC circuit are due to the transformer windings and especially due to the switching of the GTO valves [11, 12].

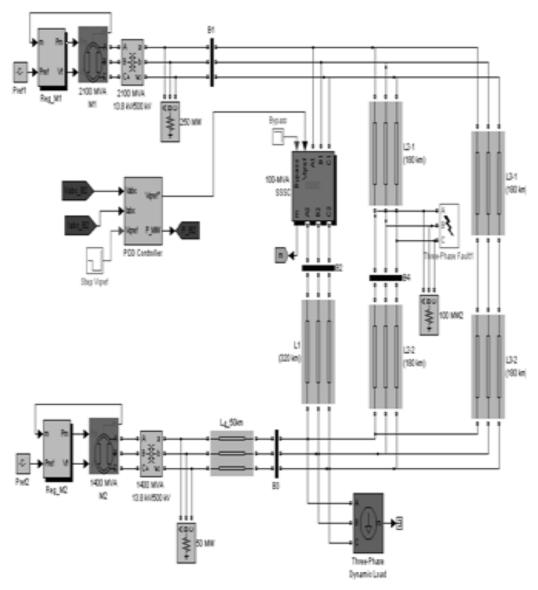

#### III. TEST SYSTEM DESCRIPTION

In this paper, the SSSC is used to damp power oscillation on a power grid following a three-phase fault. The power grid consists of two power generation substations and one major load center at bus B3. The first power generation substation (M1) has a rating of 2100 MVA; representing 6 machines of 350 MVA and the other one (M2) has a rating of 1400 MVA, representing 4 machines of 350 MVA. The load center of approximately 2200 MW is modeled using a dynamic load model where the active & reactive power absorbed by the load is a function of the system voltage. The generation substation M1 is connected to this load by two transmission lines L1, L2 and L3. L1 is 320-km long and L2 is split in two segments of 180 km in order to simulate a three-phase fault (using a fault breaker) at the midpoint of the line. The generation substation M2 is also connected to the load by a 50-km line (L4). When the SSSC is bypass, the power flow towards this major load is as follows: 664 MW flow on L1 (measured at bus B2), 563 MW flow on L2 (measured at B4) and 990 MW flow on L4 (measured at B3). The SSSC, located at bus B1, is in series with line L1.

Fig 4. Static Synchronous Series Compensator (SSSC) used for power oscillation damping

## A. Phase Control Technique for SSSC

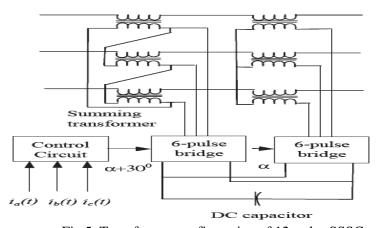

The modeled SSSC circuit with its two six-pulse VSCs and their series transformers is shown in Fig. 5. The converters are connected in series to the transmission line through two banks of lossless three-phase single-phase two-winding transformers with no saturation. The dc sides of the converters are connected in parallel and share the same dc bus. The GTO valves are switched at fundamental frequency, and the dc voltage varies according to the phase control technique used to control the output voltage.

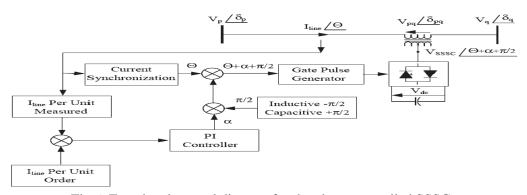

The SSSC switching is synchronized with respect to the transmission line current lline, and its rms magnitude lline is controlled by transiently changing the phase shift $\alpha$  between this current and the SSSC output voltage Vpq. The change in the phase shift  $\phi$  between the SSSC output voltage and the line current results in the change of the dc capacitor voltage Vdc, which ultimately changes the magnitude of the SSSC output voltage VSSSC and the magnitude of the transmission line current lline. A block diagram of the SSSC controller is depicted in Fig. 6.

Fig 5. Transformer configuration of 12-pulse SSSC

The SSSC output voltage VSSSC is controlled by a simple closed loop; the per unit value of the measured line current is compared with the line current per-unit order and the error of these two values is passed to the PI controller. The output of the PI controller is the angle  $\phi$ . which is added to the synchronizing signal  $\theta$  passed to the gate pulse generator by the current synchronization block. To this signal  $\theta+\phi$ , an angle of  $-\pi/2$  or  $+\pi/2$  has to be added since the SSSC output voltage is lagging or leading the line current by  $90^{\circ}$  depending on the desired capacitive or inductive operation. The phase shift of the converter output voltage SSSC V with the respect to the line current line I will cause the flow of a small amount of real power from or into the converter, thereby causing a change in the dc capacitor voltage, and consequently causing a change in the converter output voltage magnitude [5, 13].

Fig 6. Functional control diagram for the phase-controlled SSSC

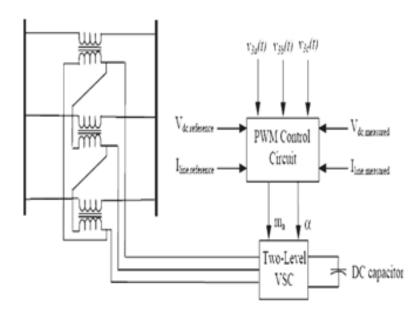

## **B.** PWM Technique

SSSC is modeled as a three-phase, PWM-controlled two-level VSC. The SSSC is modeled in detail, based on an ideal representation of the converter valves and diodes. RC parallel snubber circuits are used to reduce numerical oscillations due to switching, while a series inductance is employed at the converter output to smooth the output current. The series transformer is modeled as an ideal, three-phase, two-winding, Y- $\Delta$  connected transformer. The modeled PWM-controlled SSSC basic circuit is shown in Fig. 7

The control of the SSSC is achieved by applying SPWM control technique with a small modification. A third harmonic of appropriate amplitude is added to the sinusoidal control waveform to increase the fundamental component of the SSSC output voltage [15]. The frequency modulation ratio mf =15 is chosen to eliminate the even harmonics and moreover, since 15 is a multiple of 3, to cancel out the most dominant harmonics from the line-to-line output voltages (in the three-phase converters, only the harmonics in the line-to-line voltages are of concern).

The control and triangular waveforms are synchronized with respect to the reference voltage at left side Bus, instead to the transmission line current, which was the case for the phase controlled SSSC. The synchronizing waveforms in this case can be any voltage or current waveform; this should have no influence the controller performance. The SSSC controller uses three reference signals and consequently consists of three major control loops. The reference signals to the controller are the instantaneous three-phase voltage waveforms at mentioned Bus, the instantaneous transmission line current, and the filtered voltage at the dc terminals.

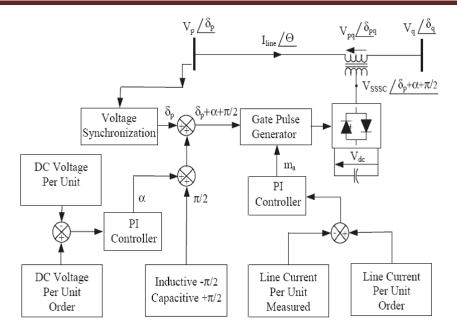

The SSSC control loops provide synchronization with the ac system voltage, maintain the dc capacitor voltage at a constant level and regulate the transmission line current. Fig. 8 show the functional control diagram, including the three control loops, of the PWM-controlled SSSC.

Fig 7. PWM-controlled basic SSSC circuit

Fig 8. Functional control diagram for the PWM-controlled SSSC

The voltage synchronization block is used to track voltage waveforms, and then, using Fourier analysis, recalculate ideal harmonic-free voltage waveforms. The control is synchronized to the voltage at that Bus, to which a  $+\pi/2$  or  $-\pi/2$  phase shift and the output of the dc voltage regulator are added. The sum of these three phase shifts provides the basic synchronizing signal  $\delta_p$  [11, 12].

#### IV. SIMULATION RESULTS AND DISCUSSION

The simulation results are divided into three sections.

Thus, Section (A) discusses results for SSSC Dynamic Response. The results obtained for the test system with a three-phase solid fault applied at Bus 4 without and with phase-controlled SSSC are presented in Section (B) and (C) respectively.

#### A. SSSC Dynamic Response

Initially  $V_{qref}$  is set to 0 pu; at t=4 s,  $V_{qref}$  is set to -0.07pu (SSSC inductive); then at t=8 s,  $V_{qref}$  is set to 0.07pu (SSSC capacitive). Also, the fault breaker will not operate during the simulation. In Fig. 9, the first graph displays the  $V_{qref}$  signal along with the measured injected voltage by the SSSC. The second graph displays the active power flow PB 2 on line L1, measured at bus B2. We can see that the SSSC regulator follows very well the reference signal Vqref. Depending on the injected voltage, the power flow on line varies. In a real system the reference signal Vqref would typically be changed much more gradually in order to avoid the oscillation.

We see on the transmitted power (PB 2 signal).so, we reduce the "Maximum rate of change for  $V_{qref}$  (pu/s)" from 4 to 0.07. A 70 Mvar 30 kV SSSC is inserted in the test system between Bus 1 and Bus 2, in series with the transmission line with higher impedance.

Fig 9. A. SSSC Dynamic Response for Reactive Power

Fig 9 .B. SSSC Dynamic Response for Voltage

## B. Test System without SSSC under a three phase fault

In this test, simulation is performed without SSSC controller. Fig. 10 indicates a three-phase fault is applied at Bus 4 that its transition times should be set as follows: [20/60 30/60]; this means that the fault will be applied at 1.33 s and will last for 10 cycles The simulation shows power oscillation.

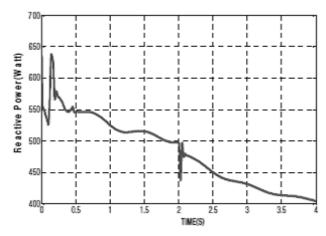

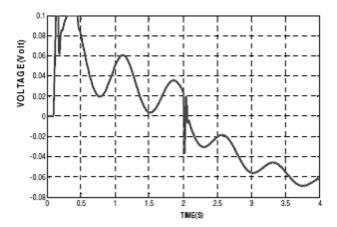

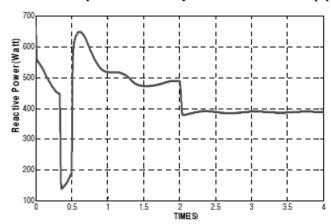

Fig 10. A. System without SSSC under a three-phase fault for Reactive Power

Fig 10. B. System without SSSC under a three-phase faultfor Voltage

#### C. Test System with SSSC under a three-phase fault

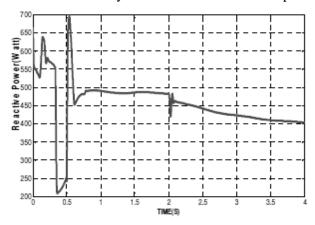

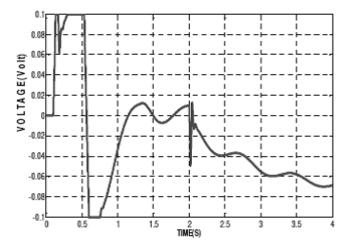

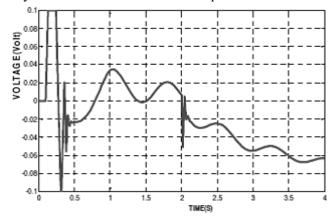

To further test the proposed SSSC controller, a three phase fault is applied at Bus 4.also, in this simulation the transition times is set as follows: [20/60 30/60]; In Fig. 11, the simulation result shows that the power oscillation on the L1 line following the three-phase fault. Moreover the performed simulation indicates that the SSSC compensator is a very effective tool to damp power oscillation.

Fig 11. A. System with SSSC under a three-phase fault for Reactive Power

Fig 11. B. System with SSSC under a three-phase fault for voltage

#### V. CONCLUSION

This paper analyzed the problem of controlling and modulating power flow in a transmission line using a Synchronous Static Series Compensator (SSSC). The studies, which include detailed techniques of twelve pulse and PWM controlled SSSC, are conducted and the control circuits are presented. The SSSC operating conditions and constraints are compared to the operating conditions of other FACTS devices, showing that the SSSC offers several advantages over others. However, at the present time the total cost of a SSSC installation is higher than the cost of other FACTS devices. Comparisons of two implemented control strategies clearly show that the PWM based and phase controller have both disadvantages and advantages, which makes the design process somewhat complicated. The dc voltage pre-set value in PWM-based controllers has to be carefully selected. As the modulation ratio lies between zero and one, the dc voltage should not be lower than the maximum of the requested SSSC output phase voltage in order to obtain proper control. On the other hand, if the dc side voltage is too high, the rating of both the GTO valves and dc capacitor has to be increased, which means higher installation costs. Not only that, a higher dc side voltage means a lower amplitude modulation ratio, and the lower modulation ratio results in higher harmonic distortion. Phase control allows the dc voltage to change according to the power system conditions, which is clearly advantageous, but it requires a more complicated controller and special and costly series transformers. Also, Simulation results validate that Voltage and Power Oscillation can be damped properly using of Synchronous Static Series Compensator (SSSC).

#### REFERENCES

- [1] "Static Synchronous Compensator," CIGRE, Working group 14.19, 1998.

- [2] N. G. Hingorani and L. Gyugyi, Understanding FACTS, Concepts and Technology of Flexible AC Transmission Systems. Piscataway, NJ: IEEE Press, 2000.

- [3] R. Mohan and R. K. Varma, Thyristor-Based FACTS Controllers for Electrical Transmission Systems. Piscataway, NJ: IEEE Press, 2002.

- [4] L. Gyugyi, N. G. Hingorani, P. R. Nannery, and N. Tai "Advanced Static Var Compensator Using Gate Turn-Off Thyristors for Utility Applications", CIGRE, 23–203, August 26 September 1, 1990, France

- [5] J. Arrillaga, B. Barrett, N. A. Vovos "Thyristor controlled Regulating Transformer for Variable Voltage Boosting", IEE Proceedings, No. 10, October 1976.

- [6] N. G. Hingorani, and L. Gyugyi "Understanding FACTS: Concepts and Technology of Flexible AC Transmission Systems", IEEE Press, 2000.

- [7] L. Sunil Kumar and A. Ghosh, "Modeling and control design of a static synchronous series compensator," IEEE Trans. Power Del., vol. 14, no. 4, pp. 1448–1453, Oct. 1999.

- [8] X.-P. Zhang, "Advanced modeling of the multi control functional static synchronous series compensator (SSSC) in Newton power flow," IEEE Trans. Power Syst., vol. 18, no. 4, pp. 1410–1416, Nov. 2003.

- [9] A. H. Norouzi and A. M. Sharaf, "An auxiliary regulator for the SSSC transient enhancement," in Proc. IEEE 35th North Amer. Power Symp., Rolla, MO, Oct. 2003.

- [10] A. H. Norouzi and A. M. Sharaf, "Two control schemes to enhance the dynamic performance of the STATCOM and SSSC," IEEE Trans. Power Del., vol. 20, no. 1, pp. 435–442, Jan. 2005.

- [11] R. Mihalic, and I, Papic "Mathematical Models and Simulation of a Static Synchronous Series Compensator", IEEE Power Tech'99 Conference, BPT99-315-42, August 1999. Budapest, Hungary.

- [12] K. K. Sen "SSSC Static Synchronous Series Compensator: Theory, Modeling, And Applications", IEEE Transactions on Power Delivery, Vol. 13, No. 1, pp. 241 246, January 1998. [13] R. Mohan and R. K. Varma, Thyristor-Based FACTS Controllers for Electrical Transmission Systems. Piscataway, NJ: IEEE Press, 2002.

- [13] M. S. El-Moursi and A. M. Sharaf," Novel Controllers for the 48-Pulse VSC STATCOM and SSSC for Voltage Regulation and Reactive Power Compensation", IEEE Transactions on Power Systems, vol.20,no.4, November 2005.

- [14] N. Mohan, T. M. Undeland, and W. P. Robbins "Power Electronics: Converters, Applications, and Design", Second Edition, John Wiley & Sons, Inc., 1995.

Page 365